# Regulations & Syllabi for DipIETE Examination (Electronics & Telecommunication)

Published under the authority of the Governing Council of The Institution of Electronics and Telecommunication Engineers 2, Institutional Area, Lodi Road, New Delhi – 110 003 (India) (2013 Edition)

Website

: http://www.iete.org

Phone

: (011) 43538800-99

Toll Free No : 18001025488

Fax

: (011) 24649429

Email

: sec.gen@iete.org, : membership@iete.org.

# Prospectus Containing Regulations & Syllabi for DipIETE Examination (Electronics & Telecommunication)

Published under the authority of the Governing Council of The Institution of Electronics and Telecommunication Engineers 2, Institutional Area, Lodi Road, New Delhi – 110 003 (India) (2013 Edition)

| Website             | : http://www.iete.org  |

|---------------------|------------------------|

| Phone               | : (011) 43538800-99    |

| <b>Toll Free No</b> | : 18001025488          |

| Fax                 | : (011) 24649429       |

| Email               | : sec.gen@iete.org,    |

|                     | : membership@iete.org. |

### CONTENTS

| 1.  | ABOUT THE INSTITUTION                                     | 1  |

|-----|-----------------------------------------------------------|----|

| 2.  | DIPIETE EXAMINATION                                       | 3  |

| 3.  | EXEMPTIONS                                                | 6  |

| 4.  | CGPA SYSTEM                                               | 6  |

| 5.  | EXAMINATION APPLICATION                                   | 7  |

| 6.  | EXAMINATION FEE                                           | 7  |

| 7.  | LAST DATE FOR RECEIPT OF EXAMINATION APPLICATION          | 8  |

| 8.  | EXAMINATION CENTRES                                       | 8  |

| 9.  | USE OF UNFAIR MEANS                                       | 9  |

| 10. | RECOUNTING                                                | 9  |

| 11. | IMPROVEMENT OF GRADES                                     | 9  |

| 12. | COURSE CURRICULUM (Electronics & Telecommunication) (ET)  |    |

|     | (Appendix-'A')                                            | 11 |

| 13. | OUTLINE SYLLABUS (ET) (Appendix-'B')                      | 13 |

| 14. | COURSE CURRICULUM (Computer Science) (CS) (Appendix-'C")  | 18 |

| 15. | OUTLINE SYLLABUS (CS) (Appendix-'D')                      | 21 |

| 16. | DETAILED SYLLABUS (Appendix-'E')                          | 26 |

| 17. | RECOGNITIONS GRANTED TO THE DIPLETE EXAMINATION BY        | 76 |

|     | GOVERNMENT OF INDIA / OTHER AUTHORITIES (Appendix-'F')    |    |

| 18. | RECOGNITIONS GRANTED TO THE Dip IETE EXAMINATION BY STATE | 77 |

|     | GOVERNMENTS (Appendix-'G')                                |    |

|     |                                                           |    |

# INTRODUCTION

The Institution of Electronics and Telecommunication Engineers (IETE), formerly the Institution of Telecommunication Engineers (ITE) was founded in 1953 by a small group of professionals for the advancement of Telecommunication and Electronics in India. Today the Institution has grown in its status to international levels with its manifold activities for furthering the cause of development in the key sectors of national economy namely Electronics, Telecommunications, Computer Science & Engineering, Information Technology and allied disciplines. The emphasis of the current activities is on creation of a concrete base of trained manpower in these fields at various levels of competence and also to contribute gainfully towards the continued professional development needs of existing technical personnel. The IETE also provides a platform for meaningful interaction among professionals from the Industry, R&D Organisations, Educational Institutions and Government Departments.

#### MEMBERSHIP

1. The IETE is a professional society devoted to the advancement of Electronics and Telecommunication, Computer Science Engineering and Information Technology. The Institution is headed by Governing Council, elected from its large base of corporate members in India and abroad. It confers professional status by way of admitting such persons, as may be qualified to various classes of membership such as Honorary Fellow, Distinguished Fellow, Fellow, Member, Associate Member, Diploma Member, Associate and Student Member. Organizational Membership is also open to Public/Private Sector Companies, Institutions, R&D Laboratories and Government Organizations.

#### OBJECTIVES

2. The IETE focuses on advancing the science and technology of electronics, telecommunications, computers, information technology and related areas. The objectives of the Institution, inter-alias includes;

- Organise conferences, symposia, workshops and brainstorming sessions involving all concerned professionals, students and industry associations for the advancement of the Disciplines.

- Provide a forum for discussion on national policies and to provide suitable inputs to policy makers.

- Promote and conduct basic engineering and continuing technical education programme for human resource development.

- Bring out quality publications for all levels of readership.

- Honour outstanding professionals.

#### EXAMINATIONS

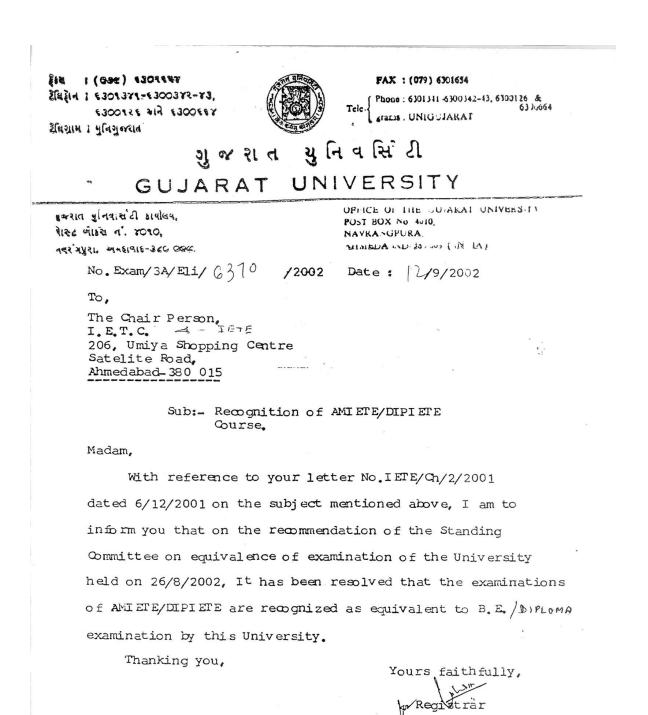

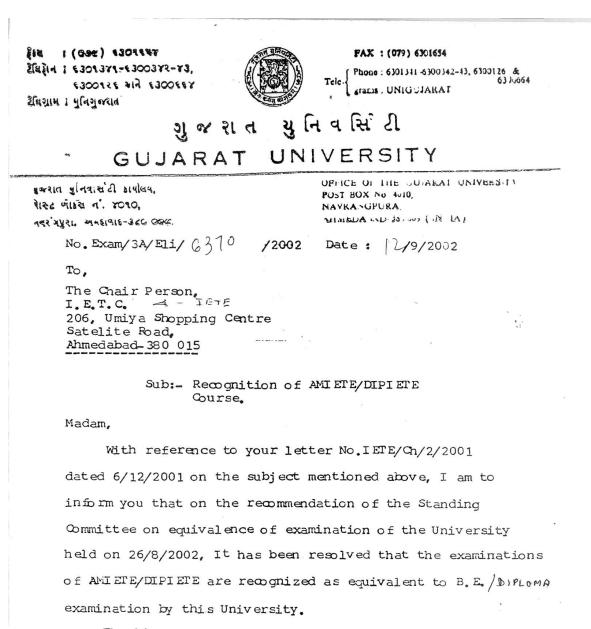

3. The IETE conducts the Diploma Level (DIPIETE) Examination, in order that a student qualifies and becomes a Diploma Member. At the time of enrolment a student is enrolled as Student Diploma (SD). On successful completion of the curriculum and clearance of requisite membership fee, he is made a Diploma member of IETE. Such members are then eligible to pursue AMIETE course without paying any enrolment fee. The DIPIETE examination is recognized by the Ministry of Human Resource Development (MHRD)- **Appendix 'F'** similar recognition has also been given by several State Governments - **Appendix 'G**'.

FACILITIES FOR STUDENTS

The IETE helps the students by extending library facilities, laboratory assistance, and 4. coordination of IETE Students Forums and by providing necessary guidance at its IETE Centres. To spread its many fold technical activities in all the regions of the country. IETE has established so far 65 Centres spread all over the country including a centre at Kathmandu and examination centre at Abhu Dhabi. IETE also has mutual arrangements with similar professional bodies like the Institution of Engineers (India), CSI, IEEE (USA), IEEE Com Soc and IET (UK) for availing each other's facilities for the benefit of its members.

#### SOLUTIONS TO QUESTION PAPERS

5. To help the students, IETE has printed solutions to Questions papers for DipIETE stream. List of subjects for which solutions are printed is available on the website www.iete.org

#### LABORATORY MANUAL

6. All students of DipIETE pursuing new scheme implemented from Jun 09 exams are required to procure lab-manuals and conduct their experiments and record the same in the concerned lab-manuals. The manuals of all the lab examination have been printed. Students can obtain these manuals as under:

- From Reception counter at IETE HQ on payment of Rs.225/- per manual without (a) CD and Rs.300/- per manual with CD.

- Through post by sending a DD in favour of Secretary General, IETE payable at (b) New Delhi towards cost of Manuals plus postal charges. The postal charge is Rs.50/- per manual.

- These manuals are also available at all IETE Centres. Students are advised to (c) approach the nearby Centre for the same.

#### **ASSISTANCE IN PLACEMENT**

7. IETE makes effort to assist in the placement of students with the help of a Placement Cell established at IETE HQ, New Delhi. RECOGNITION

The IETE is recognized by the Government of India as an EDUCATIONAL INSTITUTION 8. OF NATIONAL EMINENCE. The IETE has also been recognized by the Government of India, Ministry of Science and Technology, Dept. of Scientific and Industrial Research as a SCIENTIFIC AND INDUSTRIAL RESEARCH ORGANISATION (SIRO).

#### STUDENT INTERACTION CELL

With a view to quickly resolve student queries, a single window to address all types of 9. queries, problems and to help students, a Student Interaction Cell has been established at IETE HQ, New Delhi. This Cell is at the ground floor of the IETE HQ building. Student can approach SIC by:-

- Tel No 011-43538853 Toll free No. 18001025488 Fax : 011-24649429

- Email: sic@iete.org •

10. If the students' queries are not answered or resolved within a reasonable time, students may contact Secretary General, IETE through personal meeting or phone (011-43538821/22) or email (sec.gen@iete.org). Students are not to approach any other section of the HQ as their queries/problems shall not be entertained by them.

#### **IMPORTANT INFORMATION**

#### Students are advised to give their Mobile No. & Email ID for better and faster communication

#### DIPIETE EXMINATION

#### **REGULATIONS & SYLLABI**

#### INTRODUCTION

11. IETE conducts DIPIETE Examination in the following two streams.

(a) Electronics and Telecommunication Engineering (ET)

#### (b) Computer Science and Engineering (CS)

The block and outline syllabi of these streams are given in this booklet and detailed syllabi of (ET) stream is appended at appendix "E".

#### ELIGIBILITY

12. A candidate desirous of taking up the DIPIETE Examination should first be enrolled as

Student (D) member as per Byelaw 17 of the Institution, which is reproduced below: -

#### • Bye law 17 – Student (D) Member

Every candidate for election to the class of Student (D) shall satisfy the Council that

he/she is not less than 14 years of age and has minimum pass in Class X conducted by a

Recognised Board of Education with General Science (Physics) and Mathematics or its

equivalent as prescribed by the Council from time to time; and

- (a) is sponsored by a Corporate Member of the Institution, and either

- (b) that he/she is or has been a student of Electronics Engineering/

Telecommunication Engineering/ Electrical Engineering/ Physics/ Computer Engineering

as applicable, from a University/ College/School approved by the Council

- OR

- (c) that he/she is or has been an engineering pupil/apprentice/assistant in a

recognized firm, society or organization engaged in engineering or allied activities.

#### ENROLMENT

13 A candidate is required to apply for enrolment on the prescribed form (IETE-4), which is contained in this syllabus. The form also includes the conditions for eligibility.

#### **CORPORATE MEMBER'S RECOMMENDATION AND CERTIFICATES**

14. Every application form for student member must be proposed by a corporate member of the IETE and the copies of certificates (age, educational/experience) should be attached duly attested by a corporate member/Gazetted Officer, failing which the application shall not be entertained. For this purpose, the candidate may contact the office of the local centres of IETE. The list of corporate members is available with them. However, in case of any difficulty in getting the enrolment proposed, the form may be submitted directly to the IETE HQ for further action. **ENROLMENT FEE**

15. Fees to be paid for enrolment are as given in Form IETE-4 contained in this syllabus. The enrolment fees payable by student members are as under: -

|                                                | Member in India | Member Abroad |

|------------------------------------------------|-----------------|---------------|

|                                                | (Rs)            | (US \$)       |

| (a) Application Fee                            | 200.00          | 40.00         |

| (b) Admission Fee                              | 200.00          | 40.00         |

| (c) Building-cum-Lib. Fund                     | 1300.00         | 260.00        |

| (d) Composite Subscription<br>(for five years) | 2500.00         | 360.00        |

| (e) Lab Infrastructure Fee                     | 600.00          | 100.00        |

| (f) Development Fee                            | 500.00          | 100.00        |

| (g) Establishment Fee                          | 700.00          | 100.00        |

|                                                | 6000.00         | 1000.00       |

16. Enrolment fee is to be paid in one instalment at the time of enrolment. The student membership will be valid for 10 consecutive examinations from the date of enrolment. Thereafter, the student members not completing their DIPIETE Examination are to seek re-enrolment for further 10 examinations by remitting applicable amount before or immediately after the expiry of the membership period to continue their membership to enable them to appear in the remaining papers and complete DIPIETE. Any examination chance not availed by a student due to whatsoever reason will be counted within 10 examinations.

#### MINIMUM PERIOD OF MEMBERSHIP

17. A Student member shall be allowed to appear in the DIP IETE Examination only after he/she has been enrolled as Student (D) member with the Institution. Only those Students (D) members enrolled on or before 28/29<sup>th</sup> February and 31<sup>st</sup> August, will be allowed to appear in the next DIPIETE Examination of the Institution, held in June and December respectively. Membership should be alive at the time of submitting the examination application form.

#### TIME LIMIT TO COMPLETE DIPIETE

18. A student is required to complete DIPIETE Examination within two enrolment periods of 10 consecutive examinations each from the date of initial enrolment. The student will, therefore, be permitted to seek only one renewal of membership. Renewal is to be applied for before or immediately after the expiry of initial enrolment with continuity of enrolment maintained by the student. Any delayed re-enrolment entailing missed chances will be counted towards total number of examinations and no relaxation in this regard will be permissible. If the request for renewal is made after the stipulated period of two enrolments, admission will be treated as a fresh enrolment and no benefit in terms of exemptions in respect of subject(s) passed or exempted during the earlier enrolment will be granted. Students must renew their membership in time. Otherwise they will not be allowed to appear in the DIPIETE examination. No notice will be sent to the students for renewal of membership.

19. The course curriculum and outline Syllabi for both the streams are given as follows: -

- **Course Curriculum (ET)** (Appendix-A) (a)

- Outline Syllabus (ET) (b)

(Appendix-B)

Course Curriculum (CS) (Appendix-C) (C) **Outline Syllabus (CS)** (d)

(Appendix-D)

The detailed syllabus of the Electronics & Telecommunication stream is given at Appendix 'E'.

#### **DIPIETE EXAMINATION**

20. DIPIETE examination is divided in two Sections viz. Section A & B with a total 17 theory papers (8 in Section A and 9 in Section B) and 4 labs (2 labs in Section A and 2 labs in Section B). Each Section is divided in two parts viz. Part-I and Part-II. In addition a student has to undergo a project work, seminar and a Course in Communication Skills & Technical Writing. The course on Communication Skills & Technical Writing is mandatory but would not count towards overall CGPA.

21. Distribution of subjects is as under:

|     |       |           |    | -                                      |

|-----|-------|-----------|----|----------------------------------------|

| (a) | Secti | on A      |    |                                        |

|     | (i)   | PART-I    |    | Four subjects & 1 Lab                  |

|     | (ii)  | PART-II   |    | Four subjects & 1 Lab                  |

| (b) | Secti | Section B |    |                                        |

|     | (i)   | PART-I    |    | Five subjects & 1 Lab                  |

|     | (ii)  | PART-II   |    | Four subjects & 1 Lab                  |

|     |       |           | (2 | compulsory & 2 from elective subjects) |

- **Project Work** (C)

- (d) Seminar

#### **Course in Communication Skills & Technical Writing** (f) (Any time during the course)

22. The student should appear in Section A Part-I first and then in Part-II. If a student appears in a part in first attempt, he can appear in the subsequent part in next attempt even though he/she may not have passed in the subjects of the previous part.

Not withstanding above, a student will not be allowed to complete the curriculum in less than three years unless he has been exempted in some subjects.

#### LAB EXAMINATION

23. Eligibility for Lab, Seminar and Project Examination -

The students are advised to look into the web site www.iete.org for the eligibility criteria for appearing in the Lab, Seminar and Project examination.

#### **COMMUNICATION SKILLS & TECHNICAL WRITING**

24. The course on Communication Skills & Technical Writing is compulsory for all students. However, the course does not contribute to the overall CGPA. A minimum of 35% marks combining theory and oral test has to be obtained by the student at any time before the completion of his/her DipIETE. The student has to appear for both in one exam. (Either in June or in December) This course consists of theory and oral test. Accordingly, "PASS" or "FAIL" will be reflected in the Grade Sheet.

**Theory :** This consists of written examination for 80 marks. (a)

(b) <u>Oral Test</u>: consists of an Oral Test to test the Communication Skills which includes an oral presentation on any subject of the choice of students (e.g. About IETE, General knowledge topics etc). This presentation need not be on technical subjects. This test carries 20 marks.

#### EXEMPTIONS

25. Exemption may be granted in various papers to the students who have passed similar subjects from elsewhere or other courses. Such exemptions are granted to a candidate passing the subject and successfully completing the course/curriculum from recognized Institutions/Colleges and approved by the IETE Governing Council.

Candidates seeking exemption are required to submit the following documents along with requisite fee:

- (a) Application form for exemption.

- (b) Certificate of the course/curriculum completed by the student.

- (c) Mark sheets duly attested.

- (d) Certified copy of syllabi from which the candidate has passed the course.

- (e) Fee @ Rs. 700/- per subject for which exemption is sought.

Candidates are advised to apply for exemption, if required, at the earliest opportunity. All cases of exemptions are considered by the Academic Committee of the Institution. For all subjects where exemption are granted will be communicated to the students in the Grade sheet of the first examination after the exemption is sought as it generally takes two month to process an application for exemption. Exemption will generally be granted if the major portion of the syllabi matches with IETE Syllabus. THE DECISION OF THE ACADEMIC COMMITTEE WILL BE FINAL AND BINDING TO ALL CONCERNED. NO REPRESENTATION IN THIS RESPECT WILL BE ENTERTAINED.

#### AWARD OF DIPIETE

26. Every Student member (SD) successfully completing Sections A&B subjects including lab examinations with project work and a course in Communication Skills & Technical Writing of DIPIETE Examination as per regulations prescribed by the Governing Council from time to time shall be eligible to become a member (DipIETE). On payment of requisite fee for membership, he/she will be awarded a certificate of having passed the DIPIETE examination of the Institution and shall then be eligible for transfer to the class of DipIETE. To pass DipIETE Examination, a student is required to score a minimum

grade of 'D' having a grade point of 4 for each subject and having an aggregate of 5 CGPA. However for Project and lab examination, he/she should get a minimum grade of C having a grade point of 5.

#### CGPA SYSTEM

(a) Subject wise grade and grade points are as given below:-

| <u>Grade</u> | Grade Point |

|--------------|-------------|

| A+           | 10          |

| А            | 9           |

| B+           | 8           |

| В            | 7           |

| C+           | 6           |

| С            | 5           |

| D            | 4           |

| F,F+         | Fail        |

(b) CGPA will be calculated as under only for the subjects where a student has passed:-

$\begin{array}{rcl} \mathsf{CGPA} & = & \underbrace{C_1 \ G_1 + C_2 \ G_2 - \cdots + C_n \ G_n}_{C_1 + C_2 + C_3 - \cdots - C_n} \\ & & \\ \mathsf{Where} \ G_1 \ G_2 - \cdots - \mathsf{denote} \ \mathsf{the} \ \mathsf{grade} \ \mathsf{point} \ \mathsf{scored}. \\ & & \\ C_1 \ C_2 - \cdots - \mathsf{denote} \ \mathsf{the} \ \mathsf{credits} \ \mathsf{of} \ \mathsf{subjects}. \end{array}$

#### All theory Subjects & Lab Carry 4 Credits. Project work Carries 8 Credits.

(c) The award of division/classification will be as under :-

| (i)   | CGPA of 9 or more                | - | Distinction     |

|-------|----------------------------------|---|-----------------|

| (ii)  | CGPA 6.5 or more but less than 9 | - | First Division  |

| (iii) | CGPA 5 or more but less than 6.5 | - | Second Division |

| (iv)  | Less than 5                      | - | FAIL (No award  |

|       |                                  |   | Will be given)  |

(d) CGPA is converted into percentage with a multiplier of 9.5.

#### **EXAMINATION APPLICATION**

28. Applications to appear in any of the subjects of the DIPIETE Examination must be made on the prescribed OMR Examination Form and accompanied by the requisite examination fee. The prescribed application form is given initially free of cost along with prospectus and later on with a grade sheet where a student has appeared for an examination. OMR Examination application form can also be obtained by the students on payment of Rs. 20/- from any IETE Centre or HQ IETE. No action will be taken on an incomplete application. Students are advised to ensure that they have filled all the columns and have enclosed relevant documents. For exemptions, separate form is to be used. Generally, after the acceptance of examination form of the students, change of examination centre is not encouraged. However in exceptional cases, change of exam Centre will be allowed with an additional charge of Rs. 500/-. For any correction in the examination form after processing an additional amount of Rs 500/- will be charged as reprocessing fee.

Change of streams will be allowed with an additional charge of Rs. 600/-.

#### **EXAMINATION FEE**

29. Students are to submit their Examination Application form along with the fee as given below. The fee may get revised from time to time and the students are required to submit their application form along with the latest fee structure in force.

|      |      | The present fee structure is | given below:  |           |                        |

|------|------|------------------------------|---------------|-----------|------------------------|

|      |      |                              | In India (Rs) | Abroad (U | IS \$) Remarks         |

|      | (a)  | Theory papers/per subject    | 700.00        | 80.00     | To be deposited along  |

| with | (1.) |                              | 700.00        | 00.00     |                        |

|      | (b)  | Exemption/per subject        | 700.00        | 80.00     | exam application form. |

|      | (c)  | Written Test on              | 700.00        | 80.00     |                        |

|      |      | Communication Skills &       |               |           |                        |

|      |      | Technical Writing            |               |           |                        |

|      | (d)  | Project work                 | 1200.00       | 220.00    |                        |

|      | (e)  | Each Lab Examination         | 500.00        | 80.00     | To be deposited at     |

|      | (f)  | Oral Test on                 | 500.00        | 80.00     | respective IETE Centre |

|      |      | Communication Skills &       |               |           |                        |

|      |      | Technical Writing            |               |           |                        |

Note: (a) Fees will be charged per subject irrespective of whether it is for improvement OR re-appearance OR remaining paper OR additional paper OR exemption.

7

- (b) Examination/Exemption fee once paid are neither refundable nor transferable to a subsequent examination.

- (c) Enrolment Form, Examination Form and Exemption Form are to be sent separately with requisite fee along with each form.

#### LAST DATE FOR RECEIPT OF EXAMINATION APPLICATION

- 30. The last date for receipt of examination form duly filled in at the IETE HQ office for June/Dec examination respectively are as under:-

- Without late fee 25 Apr/25 Oct

• With late fee (of Rs.1500/-) 10 May/10 Nov.

Application received after these dates will not be considered.

#### DATE SHEET

31. The examinations are held twice a year from 15<sup>th</sup> June and 15<sup>th</sup> December and are conducted on all days including holidays and Sundays. These dates are firm and changes if any, will be notified to students along with admit cards and through our website **www.iete.org** and at the Local centre.

#### ADMIT CARD

32. Admit Cards will be sent to all the students to reach them by about 05<sup>th</sup> of June/December. Admit Cards of eligible students will also be available on our Websites www.iete.org and can be downloaded. Students will be allowed to appear for examination with these downloaded admit card along with their identity card. In the case of non-receipt of Admit-Card by above dates or the admit card not available on the website, the student must approach the concerned Examination Centre or IETE HQ and obtain permission to appear in the examination. No complaint in respect of non-receipt of Admit Card will be entertained once the Examination is over. A student is required to carry his IETE Identity Card and Admit Card issued by IETE for appearing in examination.

#### **EXAMINATION CENTRES**

33 Students should appear for all theory papers and practicals in the same Examination Centre. The Examination Centres for exams will be changed by IETE HQ only in special cases after getting the proof of documents. The Exam Centres marked as \* are closed. For latest list of examination Centres students are requested to refer to our Website <u>www.iete.org</u>

| CENTRES     | CENTRE<br>CODE | CENTRES   | CENTRE<br>CODE |

|-------------|----------------|-----------|----------------|

| Abu-Dhabi   | 17             | Kochi     | 32             |

| Ahmedabad   | 01             | Kolkata   | 04             |

| Allahabad   | 25             | Kozhikode | 52             |

| Aligarh*    | 24             | Mumbai    | 03             |

| Amravati    | 53             | Mysore    | 33             |

| Aurangabad* | 43             | Nagpur    | 37             |

| Bangalore   | 02             | Nashik    | 39             |

| Bhubaneswar | 27             | Noida     | 38             |

| Bhopal      | 36             | Palakkad  | 41             |

| Chandigarh  | 05             | Patna     | 46             |

| Chennai     | 12             | Pilani    | 30             |

| Coimbatore* | 47             | Pune      | 14             |

| Dharwad     | 49             | Raipur*   | 51             |

| Dehradun  | 26 | Rajkot             | 44 |

|-----------|----|--------------------|----|

| Delhi     | 06 | Ranchi             | 48 |

| Guwahati  | 07 | Shimla             | 45 |

| Gwalior*  | 50 | Thiruvananthapuram | 16 |

| Hyderabad | 08 | Vadodara           | 42 |

| Imphal    | 31 | Varanasi           | 13 |

| Jabalpur  | 23 | Vijayawada         | 15 |

| Jaipur    | 09 | Visakhapatnam      | 34 |

| Jammu*    | 35 |                    |    |

| Kanpur    | 10 |                    |    |

| Kathmandu | 19 |                    |    |

#### **USE OF UNFAIR MEANS**

34. If a student is found to have resorted to or made attempt to use **Unfair Means**, the Board of Examination may on receipt of report to that effect either from the Exam Superintendent or from invigilator or from the Evaluator/expert, take such action in respect of the student concerned as it thinks fit. The Examination Superintendent of the examination has absolute powers to expel the candidate from the examination hall, if in his opinion the student has adopted unfair means. The disciplinary action against the candidate may consist of punishment(s) extending from cancellation of the paper(s) to debarring from future examinations.

#### RESULTS

35. Results of the examinations will be announced on or before 10<sup>th</sup> February and 10<sup>h</sup> August for December & June examinations respectively and communicated to the candidates through Result Sheets separately. Results will be available on IETE Website <u>www.iete.org</u>

#### RECOUNTING

36. It may be noted that there is **no provision of re-evaluation** of answer books. Therefore request for re-evaluation are out rightly rejected.

Recounting of scores, if requested, can be done by paying Rs.200/- (US\$40) per subject. Requests for recounting of scores must be received at IETE HQ within 15 days from the date of announcement of results on **a separate application**.

#### **IMPROVEMENT OF GRADES**

37. A student who has passed in a subject may appear for improvement. He may take any number of chances irrespective of Grades previously obtained. If the student secures lower Grade than already secured, the original grade will hold good. Fee for improvement is Rs 500/-(US\$80) per paper. However, no improvement is permitted in Lab examination and Project work. Improvement is also allowed after completion of the examinations. After completion, students are required to give an Undertaking that they want/do not want to appear in any subject for improvement. Provisional Certificate/Certificate/final Grade Sheet will be issued only after receipt of undertaking that no improvements are required and the payment of Diploma Membership fee.

#### AWARDS FOR ACADEMIC EXCELLENCE

38. Six awards have been instituted to give incentive to student members for high level of performance in the DIPIETE Examinations.

#### LEGAL MATTERS

39. Adjudication in respect of legal cases concerning IETE HQ will be as per Bye-law 95 of the Institution which is reproduced below: -

"All Legal cases concerning IETE HQ shall lie within the jurisdiction of Delhi courts only" For more information kindly visit http://www.iete.org

#### AFFILIATION/ACCREDITATION

40. The Institution of Electronics and Telecommunication Engineers (IETE) neither recognises nor accepts affiliations of any private coaching Institute. Students in the past have reported that some private institutions claim that they run classes/coaching on behalf of IETE. It is reiterated that IETE does not authorise any private institution to run classes on behalf of IETE. Therefore IETE is not responsible for false/spurious Private Coaching Institutes.

#### CORRESPONDENCE WITH IETE HQ

41. Important announcements concerning students and examinations will be available on the website <u>www.iete.org</u> and are also published in IETE Journal of Education which is issued twice a year) to the DIPIETE Student members who have paid their subscriptions to date. For other facilities like participation in technical lectures, symposia etc. nearest IETE Centre/Sub-Centre may be contacted. All correspondence must be addressed to the Secretary General of the Institution (by designation and not by name). Remittances shall be made by way of crossed Bank Draft only. Facilities for making payments on-line will also be available shortly. Bank drafts should be drawn in favour of Secretary General, IETE, New Delhi payable at New Delhi .Cash is accepted by hand at Accounts Section at IETE HQ only .Whenever depositing fee by cash, students must obtain receipt and attach photocopy of the same along with application. MONEY ORDER WILL NOT BE ACCEPTED.

#### CHANGE OF ADDRESS

42. Students are advised to intimate their change of address to IETE HQ immediately, quoting their Membership Number, complete address with Pin Code.

Students are advised to provide their e-mail ID, telephone no and mobile no with their latest address in all correspondence.

43.

#### **MISCELLANEOUS INFORMATION**

- Acknowledgement for receipt of enrollment forms and declaration of exam results are given through SMS and Web.

- All students' related information is displayed on web site www.iete.org. and

- Students are advised to visit our web site regularly.

- All payment of fees can also be made on-line. For details refer our website <u>www.iete.org.</u>

Scheme and Structure for the Programme of DIPIETE in Electronics & Telecommunication

Appendix - "A"

|        | SECTION A          |                                               |                        |                |        |           |                                |            |                |  |  |  |  |  |  |  |  |  |  |  |    |     |       |  |                   |

|--------|--------------------|-----------------------------------------------|------------------------|----------------|--------|-----------|--------------------------------|------------|----------------|--|--|--|--|--|--|--|--|--|--|--|----|-----|-------|--|-------------------|

|        | Part - I Part - II |                                               |                        |                |        |           |                                |            |                |  |  |  |  |  |  |  |  |  |  |  |    |     |       |  |                   |

| SI     | Sub                | Title                                         | Examination<br>Credits |                |        |           |                                |            |                |  |  |  |  |  |  |  |  |  |  |  | SI | Sub | Title |  | nination<br>edits |

| N<br>O | Code               | Title                                         | Theor<br>y             | Practical<br>s | N<br>O | Code      | Title                          | Theor<br>y | Practical<br>s |  |  |  |  |  |  |  |  |  |  |  |    |     |       |  |                   |

| 1      | DE<br>101          | Engineering Mathematics - I *                 | 4                      | -              | 1      | DE<br>105 | Engineering Mathematics – II * | 4          | -              |  |  |  |  |  |  |  |  |  |  |  |    |     |       |  |                   |

| 2      | DE<br>102          | Fundamentals of Electrical &<br>Electronics * | 4                      | -              | 2      | DE<br>106 | Analog Electronics             | 4          | -              |  |  |  |  |  |  |  |  |  |  |  |    |     |       |  |                   |

| 3      | DE<br>103          | Computer Fundamentals & C<br>Programming *    | 4                      | -              | 3      | DE<br>107 | Networks & Transmission Lines  | 4          | -              |  |  |  |  |  |  |  |  |  |  |  |    |     |       |  |                   |

| 4      | DE<br>104          | Electronic Engineering Materials              | 4                      | -              | 4      | DE<br>108 | Logic Design *                 | 4          | -              |  |  |  |  |  |  |  |  |  |  |  |    |     |       |  |                   |

| 5      | DE<br>141          | C Programming Lab                             | -                      | 4              | 5      | DE<br>142 | Analog Electronics Lab         | -          | 4              |  |  |  |  |  |  |  |  |  |  |  |    |     |       |  |                   |

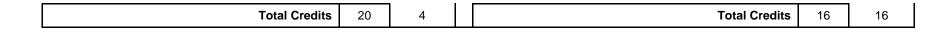

|        |                    | Total Credits                                 | 16                     | 4              |        |           | Total Credits                  | 16         | 4              |  |  |  |  |  |  |  |  |  |  |  |    |     |       |  |                   |

All the students have to pass a course in "Communication Skills & Technical Writing" which will not be counted for the overall percentage

| DE  | Communication Skills & Technical | 30 |          |

|-----|----------------------------------|----|----------|

| 137 | Writing(Oral)*                   |    | Marks    |

| DE  | Communication Skills & Technical | 70 | Marks    |

| 138 | Writing(Written)*                | 10 | IVIATIKS |

|                                            |                                                                             |                                                              |         | SI           | ECTION                      | В                                                                           |                                        |          |              |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------|---------|--------------|-----------------------------|-----------------------------------------------------------------------------|----------------------------------------|----------|--------------|--|--|

| Part - I                                   |                                                                             |                                                              |         |              |                             | Part - II                                                                   |                                        |          |              |  |  |

| S                                          | Sub                                                                         | Title                                                        | Examina | tion Credits | S                           | Sub                                                                         | Title                                  | Examinat | tion Credits |  |  |

| Ν                                          | Code                                                                        |                                                              | Theory  | Practicals   | Ν                           | Code                                                                        |                                        | Theory   | Practicals   |  |  |

| 1                                          | DE<br>109                                                                   | Electronic Instrumentation &<br>Measurements                 | 4       | -            | 1                           | DE<br>114                                                                   | Digital Communications                 | 4        | -            |  |  |

| 2                                          | DE<br>110                                                                   | Power Electronics                                            | 4       | -            |                             | DE<br>115                                                                   | Embedded Systems                       | 4        | -            |  |  |

| 3                                          | DE<br>111                                                                   | Microprocessors &<br>Microcontrollers*                       | 4       | -            | 2                           |                                                                             | Elective – I ( from Group A)           | 4        | -            |  |  |

| 4                                          | DE<br>112                                                                   | Analog Communications                                        | 4       | -            | 3                           |                                                                             | Elective – II ( from Group B)          | 4        | -            |  |  |

| 5                                          | DE<br>113                                                                   | Telecommunication Switching<br>Systems                       | 4       | -            | 4                           | DE<br>144                                                                   | Analog & Digital Communications<br>Lab | -        | 4            |  |  |

| 6                                          | DE<br>143                                                                   | Logic Design Lab                                             | -       | 4            | 5                           | DE<br>135                                                                   | Project Work ;                         | -        | 8            |  |  |

|                                            |                                                                             |                                                              |         |              | 6                           | DE<br>136                                                                   | Seminar                                | -        | 4            |  |  |

|                                            | Total Credits                                                               |                                                              |         | 4            | Total Credits 16            |                                                                             |                                        |          | 16           |  |  |

|                                            | GROUP A<br>Students can chose any<br>one of the following elective subjects |                                                              |         |              |                             | GROUP B<br>Students can chose any<br>one of the following elective subjects |                                        |          |              |  |  |

| Stu                                        | dents ca                                                                    | n choose any one of the following a<br>an Elective I subject | as      |              | S                           | Students can choose any one of the following as an<br>Elective II subject   |                                        |          |              |  |  |

| S<br>N                                     | Sub<br>Code                                                                 | Title                                                        |         |              | S<br>N                      | Sub<br>Code                                                                 | Title                                  |          |              |  |  |

| 1                                          | DE<br>116                                                                   | Wireless & Mobile Systems                                    |         |              | 1                           | DE<br>120                                                                   | Control Engineering                    |          |              |  |  |

| 2                                          | DE<br>117                                                                   | Television Engineering and<br>Broadcasting                   |         |              | 2                           | DE<br>121                                                                   | Verilog HDL and VLSI Design            |          |              |  |  |

| 3                                          | DE<br>118                                                                   | Data Communication & Networks **                             |         |              | 3                           | DE<br>122                                                                   | Object Oriented Programming with C+-   | + **     |              |  |  |

| 4 DE<br>119 Advanced Communication Systems |                                                                             |                                                              | 4       | DE<br>123    | Java and Web Programming ** |                                                                             |                                        |          |              |  |  |

|                                            |                                                                             |                                                              |         |              |                             |                                                                             | Common to ET / CS Streams              |          |              |  |  |

#### OUTLINE SYLLABUS DIPIETE (ELECTRONICS & TELECOMMUNICATION Appendix 'B'

#### DE 101 ENGINEERING MATHEMATICS – I

- Differential Calculus

- Integral Calculus

- Linear Algebra

- Differential Equations

- Algebra

- Trigonometry

- Coordinate Geometry

#### DE 102 FUNDAMENTALS OF ELECTRICAL AND ELECTRONICS

- Electromagnetism

- DC Circuits and AC Circuits

- DC Motor

- Transformer and Induction Motor

- Basic Semiconductor and PN Junctions

- Semiconductor Diodes

- Diode Applications

- Bipolar Junction Transistor

- BJT Biasing

- Amplifiers and Oscillators

#### DE 103 COMPUTER FUNDAMENTALS & C PROGRAMMING

- Computer Basics

- Data Representation

- Input / Output Units

- Computer Languages

- Operating Systems

- Microcomputers

- Computer Networks

- Constants, Variables and Data Types

- Operators and Expressions

- Managing Input and Output Operations

- Decision Making and Branching

- Decision Making and Looping

- Arrays

- User Defined Functions

- Pointers

- File Management

#### DE 104 ELECTRONIC ENGINEERING MATERIALS

- Conducting Materials

- Dielectric Properties of Materials in Static Fields

- Dielectric Materials in Alternating Fields

- Magnetic Materials

- Semi conducting Materials

- Semi conducting Devices

- Materials for Electronic Components

- Fabrication of Semiconductors

#### DE 104 C PROGRAMMING LAB

#### DE 105 ENGINEERING MATHEMATICS – II

- Differential Calculus

- Integral Calculus

- Complex Numbers

- Vector Algebra

- Linear Differential Equations of Higher order

- Infinite Series

- Laplace Transforms

# DE 106 ANALOG ELECTRONICS

- Integrated Circuit Fabrication

- AC Analysis of BJT Circuits

- Field Effect Transistors

- Power Amplifiers

- Optoelectronic Devices

- Operational Amplifier

- Operational Amplifier Characteristics

- Operational Amplifier

Applications

- Comparators and Waveform Generators

- 555 Timer Applications

- Voltage Regulators

- DAC and ADC

# DE 107 NETWORKS AND TRANSMISSION LINES

- Laplace Transformation

- Network Theorems

- Network Parameters

- Resonance Circuits and Selectivity

- Transmission Lines

- Open and Short-Circuited Lines

- Line with any Termination

- Ultra High Frequency Lines

- Filters and Attenuators

## DE 108 LOGIC DESIGN

- Introductory Concepts

- Number Systems and Codes

- Describing Logic Circuits

- Combinational Logic Circuits

- Flip-Flops and Applications

- Digital Arithmetic Operations and Circuits

- MSI Logic Circuits

- Flip-Flops and Applications

- Counters and Registers

- Synchronous Counter Design

- Memory Devices

#### DE 142 ANALOG ELECTRONICS LAB

#### DE109 ELECTRONIC INSTRUMENTATION AND MEASUREMENTS

- Measurement Fundamentals

- Measurement of Resistance, Inductance and capacitance

- Instruments to measure Current and Voltages

- Digital measuring Instruments

- Signal Generators and Oscilloscope

- Signal Analysis Instruments and R.F Power measurement Techniques

- Recorders

- Transducers and Data Acquisition System

## DE 110 POWER ELECTRONICS

- Power Electronics

- Power Diodes

- Power Transistors

- Thyristor Devices

- Single-Phase Controlled Rectifiers

- Three-Phase Controlled Rectifiers

- DC Choppers

- Inverters

- AC Voltage Controller

- Static Switches

# DE 111 MICORPROCESSORS & MICROCONTROLLERS

- Introduction to Microprocessors

- Assembly Language Programs

- Interrupts in 8085

- Programs Using Interface Modules

- Intel 8259A- Programmable

Interrupt Controller

- Intel 8253 Programmable Interval Timer

- 8051 Microcontroller

# DE 112 ANALOG COMMUNICATIONS

- Introduction to Communication Systems

- Noise

- Amplitude Modulation

- Single-Sideband Techniques

- Frequency Modulation

- Radio Receivers

- Radiation and Propagation of Waves

- Waveguides, Resonators and Components

- Antennas

- Pulse Communications

- Broadband Communications Systems

# DE 111 TELECOMMUNICATION SWITCHING SYSTEMS

- Switching Systems

- Telecommunications Traffic

- Switching Networks

- Time Division Switching

- Control of Switching Systems

- Signaling

- Packet Switching

- Networks

#### DE 143 LOGIC DESIGN LAB

DE 134 PROJECT WORK: PHASE - I

# DE 114 DIGITAL COMMUNICATIONS

- Introduction

- Fundamental Limits on Performance

- Sampling Process

- Waveform Coding Techniques

- Base-Band Shaping for Data

Transmission

- Digital Modulation Techniques

- Detection and Estimation

- Spread Spectrum Modulation

- Applications

## DE115 EMBEDDED SYSTEMS

- Introduction to Embedded

Systems

- Custom Single Purpose

Processors: Hardware

- General Purpose Processors: Software

- Standard Single-Purpose Processors: Peripherals

- Memory

- Interfacing

- Introduction to Real Time

Operating Systems

- Case Studies of Programming with RTOS

#### ELECTIVE - I ELECTIVE - II

## DE 144 ANALOG & DIGITAL COMMUNICATIONS LAB

DE 135 PROJECT WORK:

PHASE – II DE 136 SE

DE 136 SEMINAR

#### DE116 WIRELESS & MOBILE SYSTEMS

- Introduction

- Channel Coding and Error Control

- Mobile Radio Propagation

- Cellular Concept

- Multiple Radio Access

- Multiple Division Techniques for traffic Channels

- Traffic Channel Allocation

- Mobile Communication Systems

- Existing Wireless Systems

- Satellite Systems

- Ad Hoc Networks

- Sensor Networks

- Recent Advances

- Wireless LANs, MANs and PANs

## DE 117 TELEVISION ENGINEERING & BROADCASTING

• Elements of Television System, Analysis, Synthesis of Television Pictures and Composite Video Signal

- Signal Transmission and Channel

Bandwidth

- Television Picture Tubes and Camera Tubes

- Basic Television Broadcasting and Reception

- Video Section

- Sound Section

- Vertical and Horizontal Deflection Circuits

- Colour Television

- Television Applications

# DE 118 DATA COMMUNICATION & NETWORKS

- Data Communications, Data Networking, and the Internet

- Data Transmission

- Transmission Media

- Protocol Architecture, TCP/IP, and Internet-Based Applications

- Signal Encoding Techniques

- Digital Data Communication

Techniques

- Data Link Control Protocols

- Multiplexing

- Circuit Switching and Packet Switching

- Routing in Switched Networks

- Congestion Control in Data Networks

- Local Area Network Overview

- High-Speed LANs

- Wireless LANs

- Internetwork Protocols

- Internetwork Operation

- Transport Protocols

#### DE 119 ADVANCED COMMUN ICATION SYSTEMS

- Optical Fiber Transmission Media

- Cellular Telephone Concepts

- Cellular Telephone Systems

- Introduction to Data Communications and Networking

- Fundamental Concepts of Data

Communications

- Data-Link Protocols and Data Communication Networks

- Satellite Communications

- Satellite Multiple Accessing Arrangements

## DE 120 CONTROL ENGINEERING

- Modeling of Systems

- Block Diagrams and Signal Flow Graphs

- Feedback Characteristics of Control Systems

- Control Systems and Components

- Time Response Analysis

- Concepts of Stability

- Root Locus Technique

- Frequency Domain Analysis

- Stability in Frequency Domain

- Nyquist Analysis

- Compensation

# DE 121 VERILOG HDL AND VLSI DESIGN

- Overview of Digital Design with Verilog HDL

- Gate Level and Dataflow

Modeling

- Behavioral Modeling

- Tasks and Functions

- A Review of Microelectronics and an Introduction to MOS Technology

- Basic Electrical Properties of MOSA Circuits

- MOS Circuit Design Processes

- Practical Aspects and Testability

#### DE 122 OBJECT ORIENTED PROGRAMMING WITH C++

- Object-oriented Programming Concepts

- Language Constructs

- Advanced Constructs

- Classes in C++

- Member Functions

- Operator Overloading

- Constructors and Destructors

- Inheritance

- Multiple Inheritance

- Polymorphism

- Handling Exceptions

- Templates

- C++ I/O

# DE 123 JAVA & WEB PROGRAMMING

- Java Evolution

- Overview of Java Language

- Constants, Variables, and Data Types

- Operators and Expressions

- Decision Making and Branching

- Decision Making and Looping

- Classes, Objects and Methods

- Arrays, Strings and Vectors

- Interfaces: Multiple Inheritance

- Packages: Putting Classes Together

- Multithreaded Programming

- Managing Errors and Exceptions

- Managing Input/Output Files in Java

- Web Basics and Overview

- Creating Web Pages: XHTML

- Advanced XHTML

- Design Basics

- Information Architecture and Page Layout

- CSS, Forms and form

Processing

- Client –Side Scripting: JavaScript

## DE 137 (ORAL) COMMUNICATION SKILLS AND DE 138 (WRITTEN) TECHNICAL WRITING

- Communication: Its Types and Significance

- Grammar

- Syntax

- Reading Skills

- Writing Skills

- Listening Skills

- Speaking Skills

- Technical Report and Scientific Report

- Campus Recruitment, Interview

and Group Discussion

- Meeting Negotiations, Phone and Mobile Phone Skills

#### Scheme and Structure for the Programme of DIPIETE in Computer Science & Engineering

#### Appendix - "C"

|              |           |                                               |                        | SI             | ECTION | Α         |                                      |                        |                |  |  |

|--------------|-----------|-----------------------------------------------|------------------------|----------------|--------|-----------|--------------------------------------|------------------------|----------------|--|--|

|              | Part - I  |                                               |                        |                |        |           | Part - II                            |                        |                |  |  |

| SI<br>N<br>o | Sub       | Title                                         | Examination<br>Credits |                | SI     | Sub       |                                      | Examination<br>Credits |                |  |  |

|              | Code      |                                               | Theor<br>y             | Practical<br>s | N<br>O | Code      | Title                                | Theor<br>y             | Practical<br>s |  |  |

| 1            | DC<br>101 | Engineering Mathematics – I *                 | 4                      | -              | 1      | DC<br>105 | Engineering Mathematics – II *       | 4                      | -              |  |  |

| 2            | DC<br>102 | Fundamentals of Electrical &<br>Electronics * | 4                      | -              | 2      | DC<br>106 | Object Oriented Programming with C++ | 4                      | -              |  |  |

| 3            | DC<br>103 | Computer Fundamentals & C<br>Programming *    | 4                      | -              | 3      | DC<br>107 | Computer Organization                | 4                      | -              |  |  |

| 4            | DC<br>104 | Data Structures                               | 4                      | -              | 4      | DC<br>108 | Logic Design *                       | 4                      | -              |  |  |

| 5            | DC<br>141 | C & Data Structures Lab                       | -                      | 4              | 5      | DC<br>142 | OOPS Lab                             | -                      | 4              |  |  |

|              |           | Total Credits                                 | 16                     | 4              |        |           | Total Credits                        | 16                     | 4              |  |  |

All the students have to pass a course in "Communication Skills & Technical Writing" which will not be counted for the overall percentage

| Γ | DC  | Communication Skills & Technical | 30 |          |

|---|-----|----------------------------------|----|----------|

|   | 137 | Writing(Oral)*                   |    | Marks    |

| ſ | DC  | Communication Skills & Technical | 70 | Marks    |

|   | 138 | Writing(Written)*                | 70 | IVIAI KS |

|          |               |                                             |                        | SI             | ECTION | В         |                               |                        |                |  |

|----------|---------------|---------------------------------------------|------------------------|----------------|--------|-----------|-------------------------------|------------------------|----------------|--|

| Part - I |               |                                             |                        |                |        | Part - II |                               |                        |                |  |

| SI       | Sub<br>Code   | Title                                       | Examination<br>Credits |                | SI     | Sub       |                               | Examination<br>Credits |                |  |

| N<br>O   |               |                                             | Theor<br>y             | Practical<br>s | N<br>O | Code      | Title                         | Theor<br>y             | Practical<br>s |  |

| 1        | DC<br>109     | Analysis & Design of Information<br>Systems | 4                      | -              | 1      | DC<br>114 | Data Communication & Networks | 4                      | -              |  |

| 2        | DC<br>110     | Operating Systems & Systems<br>Software     | 4                      | -              | 2      | DC<br>115 | Software Engineering          | 4                      | -              |  |

| 3        | DC<br>111     | Microprocessors & Microcontrollers *        | 4                      | -              | 3      |           | Elective – I( from Group A)   | 4                      | -              |  |

| 4        | DC<br>112     | Database Management Systems                 | 4                      | -              | 4      |           | Elective – II( from Group B)  | 4                      | -              |  |

| 5        | DC<br>113     | Java & Web Programming                      | 4                      | -              | 5      | DC<br>144 | DBMS Lab                      | -                      | 4              |  |

| 6        | DC<br>143     | Java & Web Programming Lab                  | -                      | 4              | 6      | DC<br>135 | Project Work: Phase - II      | -                      | 8              |  |

|          |               |                                             |                        |                | 7      | DC<br>136 | Seminar                       | -                      | 4              |  |

|          | Total Credits |                                             |                        | 4              |        |           | Total Credits                 | 16                     | 16             |  |

| Stu          | GROUP A<br>Students can chose any<br>one of the following elective subjects<br>Students can choose any one of the following as<br>an Elective I subject |                                   |  |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|--|

| SI<br>N<br>o | N Code Title                                                                                                                                            |                                   |  |  |  |  |  |  |

| 1            | DC<br>116                                                                                                                                               | Computer Graphics & Visualization |  |  |  |  |  |  |

| 2            | DC<br>117                                                                                                                                               | C# & .Net                         |  |  |  |  |  |  |

| 3            | DC<br>118                                                                                                                                               | Internet Applications             |  |  |  |  |  |  |

| 4            | DC<br>119                                                                                                                                               | Cloud Computing                   |  |  |  |  |  |  |

| GROUP B<br>Students can chose any<br>one of the following elective subjects<br>Students can choose any one of the following as<br>Elective II subject |              |                                 |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|--|--|--|--|--|

| SI<br>N<br>o                                                                                                                                          | N Code Title |                                 |  |  |  |  |  |

| 1                                                                                                                                                     | DC<br>120    | Software Testing                |  |  |  |  |  |

| 2                                                                                                                                                     | DC<br>121    | Embedded Systems **             |  |  |  |  |  |

| 3                                                                                                                                                     | DC<br>122    | Mobile Applications Development |  |  |  |  |  |

| 4                                                                                                                                                     | DC<br>123    | Network Management              |  |  |  |  |  |

| Э. |

|----|

| Э. |

Common to ET / CS Streams Syllabus same as that of core subject for DIPIETE -ET \*

\*\*

#### OUTLINE SYLLABUS Appendix 'D' DIPIETE (COMUTER SCIENCE & ENGINEERING)

#### DC 101 ENGINEERING MATHEMATICS – I

- Differential Calculus

- Integral Calculus

- Linear Algebra

- Differential Equations

- Algebra

- Trigonometry

- Coordinate Geometry

#### DC 102 FUNDAMENTALS OF ELECTRICAL AND ELECTRONICS

- Electromagnetism

- DC Circuits and AC Circuits

- DC Motor

- Transformer and Induction Motor

- Basic Semiconductor and PN Junctions

- Semiconductor Diodes

- Diode Applications

- Bipolar Junction Transistor

- BJT Biasing

- Amplifiers and Oscillators

#### DC 103 COMPUTER FUNDAMENTALS & C PROGRAMMING

- Computer Basics

- Data Representation

- Input / Output Units

- Computer Languages

- Operating Systems

- Microcomputers

- Computer Networks

- Constants, Variables and Data Types

- Operators and Expressions

- Managing Input and Output Operations

- Decision Making and Branching

- Decision Making and Looping

- Arrays

- User Defined Functions

- Pointers

- File Management

#### DC 104 DATA STRUCTURES

- Advanced C Concepts

- Recursion

- Structures, Union and Files

- Arrays, Searching and Sorting

- Stacks and Queues

- Liked Lists

- Trees

- Graphs

#### DC 141 C& DATA STRUCTURES LAB

### DC 105 ENGINEERING MATHEMATICS – II

- Differential Calculus

- Integral Calculus

- Complex Numbers

- Vector Algebra

- Linear Differential Equations of Higher order

- Infinite Series

- Laplace Transforms

#### DC 106 OBJECT ORIENTED PROGRAMMING WITH C++

- Object-Oriented Programming Concepts

- Language Constructs

- Advanced Constructs

- Classes in C++

- Member Functions

- Operator Overloading

- Constructors and Destructors

- Inheritance

- Multiple Inheritance

- Polymorphism

- Handling Exceptions

- Templates

- C++ I/O

## DC 107 COMPUTER ORGANIZATION

- Basic Structure of Computers

- Machine Instructions and Programs

- Input/Output Organization

- Memory System

- Arithmetic

- Basic Processing Unit

# DC 108 LOGIC DESIGN

- Introductory Concepts

- Number Systems and Codes

- Describing Logic Circuits

- Combinational Logic Circuits

- Flip-Flops and Applications

- Digital Arithmetic Operations and Circuits

- MSI Logic Circuits

- Flip-Flops and Applications

- Counters and Registers

- Synchronous Counter Design

- Memory Devices

# DC 142 OOPS LAB

#### DC 109 ANALYSIS & DESIGN OF INFORMATION SYSTEMS

- The Context of Systems Analysis & Design Methods

- Information System Building Blocks

- Information Systems Development

- Systems Analysis

- Modeling System Requirements with Use Cases

- Data Modeling and Analysis

- Object-Oriented Analysis and Modeling Using the UML

- Systems Design

- User-Interface Design

- Object-Oriented Design and Modeling Using the UML

- Systems Construction and Implementation

- Systems Operations and Support

# DC 110 OPERATING SYSTEMS & SYSTEMS SOFTWARE

- Evolution of OS Functions

- Processes

- Scheduling

- Deadlocks

- Process Synchronization

- File Systems

- Memory Management

- Language Processors

- Data Structures for Language

Processing

- Scanning and Parsing

- Macros and Macro Processors

- Linkers

- Assemblers

- Compilers and Interpreters

# DC 111 MICORPROCESSORS & MICROCONTROLLERS

- Introduction to Microprocessors

- Assembly Language Programs

- Interrupts in 8085

- Programs Using Interface

Modules

- Intel 8259A- Programmable

Interrupt Controller

- Intel 8253 Programmable Interval Timer

- 8051 Microcontroller

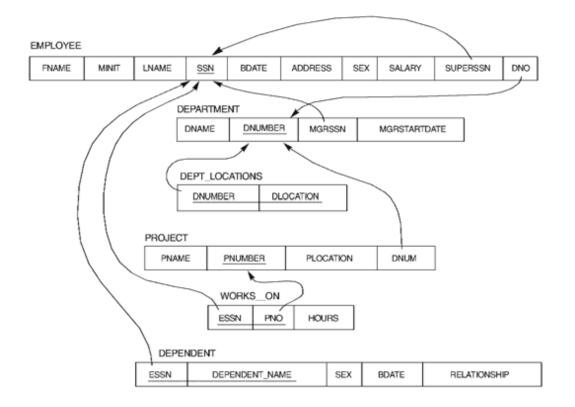

#### DC 112 DATABASE MANAGEMENT SYSTEMS

- Databases and Database Users

- Database System Concepts and Architecture

- Data Modeling Using the Entity-Relationship Model

- The Enhanced Entity-Relationship (EER) Model

- The Relational Data Model and Relational Database Constraints

- The Relational Algebra and Relational Calculus

- Relational Database Design By ER - to - Relational Mapping

- SQL-99: Schema Definition, Constraints, Queries and Views

- Relational Database Design

- Transaction Processing Concepts

# DC 113 JAVA & WEB PROGRAMMING

- Java Evolution

- Overview of Java Language

- Constants, Variables, and Data Types

- Operators and Expressions

- Decision Making and Branching

- Decision Making and Looping

- Classes, Objects and Methods

- Arrays, Strings and Vectors

- Interfaces: Multiple Inheritance

- Packages: Putting Classes Together

- Multithreaded Programming

- Managing Errors and Exceptions

- Managing Input/Output Files in Java

- Web Basics and Overview

- Creating Web Pages: XHTML

- Advanced XHTML

- Design Basics

- Information Architecture and Page Layout

- CSS, Forms and Form

Processing

- Client-Side Scripting: Javascript

#### DC 143 JAVA & WEB PROGRAMMING LAB

#### DC 134 PROJECT WORK: PHASE – I

# DC 114 DATA COMMUNICATION & NETWORKS

- Data Communications, Data Networking, and the Internet

- Data Transmission

- Transmission Media

- Protocol Architecture, TCP/IP, and Internet-Based Applications

- Signal Encoding Techniques

- Digital Data Communication Techniques

- Data Link Control Protocols

- Multiplexing

- Circuit Switching and Packet

Switching

- Routing in Switched Networks

- Congestion Control in Data Networks

- Local Area Network Overview

- High-Speed LANs

- Wireless LANs

- Internetwork Protocols

- Internetwork Operation

- Transport Protocols

## DC 115 SOFTWARE ENGINEERING

- Socio-Technical Systems

- Software Processes

- Project Management

- Software Requirements

- Requirements Engineering

Processes

- System Models

- Rapid Software Development

- Formal Specification

- Architectural Design

- Distributed Systems

Architectures

- Objected-Oriented Design

- Software Reuse

- Component-Based Software

Engineering

- User Interface Design

- Verification and Validation

- Software Testing

- Quality Management

- Configuration Management

## ELECTIVE - I

- ELECTIVE II

- DC 144 DBMS LAB

DC 135 PROJECT WORK: PHASE – II

DC 136 SEMINAR

# DC 116 COMPUTER GRAPHICS & VISUALIZATION

- A Survey of Computer Graphics

- Overview of Graphics Systems

- Graphics Output Primitives

- Attributes of Graphics Primitives

- Geometric Transformations

- Viewing

- Visible-Surface Detection Methods

- Illumination Models and Surface-Rendering Methods

- Interactive Input Methods and Graphical User Interfaces

- Computer Animation

# DC 117 C# & .NET

- Introducing C# and the .Net Platform

- The Philosophy of .Net

- Building C# Applications

- Core C# Programming Constructs

- Defining Encapsulated Class Types

- Understanding Inheritance and Polymorphism

- Understanding Structured Exception Handling

- Understanding Object Lifetime

• Working with Interfaces

#### DC 118 INTERNET APPLICATIONS

- Hypertext Markup Language

- More HTML

- Cascading Stylesheets

- An Introduction to Javascript

- Objects in Javascript

- Dynamic HTML with Javascript

- Programming in PERL 5

- CGI Scripting

- Building Web Applications with PERL

- An Introduction to PHP

- Building Web Applications with PHP

- XML: Defining Data for Web Applications

# DC 119 CLOUD COMPUTING

- Cloud Computing Basics

- Your Organization and Cloud Computing

- The Business Case for Going to the Cloud

- Cloud Computing Technology

- Cloud Computing at Work

- Migrating to the Cloud

- Best Practices and the Future of Cloud Computing

## DC 120 SOFTWARE TESTING

- Introduction

- Testing and Levels

- Transaction Flow Testing

- Data Flow Testing

- Domain Testing

- Paths, Path Products

- Logic Based Testing

- Testing of Object-Oriented Systems

# DC 121 EMBEDDED SYSTEMS

- Introduction to Embedded

Systems

- Custom Single Purpose

Processors: Hardware

- General Purpose Processors: Software

- Standard Single-Purpose Processors: Peripherals

- Memory

- Interfacing

- Introduction to Real Time Operating Systems

- Case Studies of Programming with RTOS

# DC 122 MOBILE APPLICATION DEVELOPMENT

- Introduction to Android

- Activities and Intents

- Introducing Android User

Inferface

- Designing User Interface Using Views

- Displaying Pictures and Menus with Views

- Data Persistence

- Content Providers

- Messaging and Networking

- Location Based Services

- Android Services

- Hardware Sensors

#### DC 123 NETWORK MANAGEMENT

- Data Communications and Network Management Overview

- SNMP and Network Management Basic Foundations: Standards, Models and Language

- SNMPv1 Network Management: Organization and Information Models

- SNMPv1 Network Management: Communication and Functional Models

- SNMP Management: RMON

- Network Management Tools, System and Engineering

- Network Management Applications

- Broadband Network Management

#### DC 137 (ORAL) DC 138 (WRITTEN) COMMUNICATION SKILLS AND TECHNICAL WRITING

- Communication: Its Types and Significance

- Grammar

- Syntax

- Reading Skills

- Writing Skills

- Listening Skills

- Speaking Skills

- Technical Report and Scientific Report

- Campus Recruitment, Interview

and Group Discussion

- Meeting Negotiations, Phone and Mobile Phone Skills

#### Appendix 'E'

#### DETAILED SYLLABUS

#### Introduction

Most of the Student Members of the IETE are working engineers/ technicians/science graduates and under graduates. Thus, due to occupational reasons and other factors these students are deprived of a formal education and therefore have to learn the subjects through self-study only.

#### **Review of Syllabus**

2. IETE periodically reviews the syllabi of DIPIETE and the aim of these reviews is not only to renovate and modernize the contents but also to make them contemporary. The syllabi for both Electronics & Telecommunications (ET) and Computer Science & Engineering (CS) streams have been reviewed recently.

3. Keeping the above aspects in view and based on feed backs/suggestions received from the students, this syllabus has been formulated to meet the following criteria:-

- The Syllabus should cater to the technological advancements.

- The textbooks should be available and affordable to the students.

- In the absence of a formal coaching to the students, there should be a reasonable correlation between the topics in a subject and the textbooks.

#### Salient Features

- 4. Some salient features of the syllabus are:-

- Each subject has a code preceding it (Viz DE101 and DC101 are codes for Mathematics I in ET & CS streams respectively).

- In order to guide the student and to enable him/her to prepare well for an examination, each subject is divided into 8 units and each unit has the course contents to be covered in 7 or 8 hours.

- The textbooks have been numbered in Roman Numerical (viz I, II, III)

- The chapters and sections are mentioned inside the bracket e.g. I (2.1) would indicates chapter 2 and section 1 of textbook I.

#### Scheme of the Examination

- 5. For all theory subjects the Question Paper contains

- 10 objective questions for 20 marks covering the complete syllabus

- 8 questions are from each unit and each question carries 16 marks.

6. Regular feed back from the students, academicians, corporate members and professionals is requested to keep this syllabus updated, so that our students keep abreast of latest technological changes. Though every effort has been made to identify standard and best textbooks for each subject, we welcome suggestions on availability of better and cheaper textbooks.

#### DE 101 **ENGINEERING MATHEMATICS – I**

#### UNIT I

#### **DIFFERENTIAL CALCULUS**

Limits: Left hand and Right hand Limits: Continuity of functions: Evaluation of simple limits: Differentiability of a Function; Geometrical Meaning of derivative; Standard Results: Logarithmic Differentiation; Differentiation of Implicit function; Parametric Equations; Successive differentiation; Calculation of n<sup>th</sup> derivative of standard functions; Leibnitz theorem for the n<sup>th</sup> derivative of the product of two functions; Applications of differentiation -Increasing and Decreasing functions; Maxima and Minima.

I (1.6, 1.8, 1.9, 1.10, 2.3, 2.25, 2.26, 2.27, 2.30, 2.31, 2.37, 4.1, 4.2) UNIT II

#### **INTEGRAL CALCULUS**

Introduction; Definitions; Hyperbolic functions; Standard results - Indefinite Integrals; Integration by the Method of Substitution; Standard formula; Integration by parts; Integration by Partial Fraction Method; Integration of Irrational Functions; Integration of Trignometric functions; Definite Integrals - Introduction; Theorems on Definite Integrals. I (21.1, 21.2, 21.4, 21.5, 22.1, 22.2, 23.1, 24.1, to 24.7, 25. 1 to 25.6, 26.1 to 26.3, 28.1, 28.2)